This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

# **Preliminary Information**

**Features**

Programmable gain, network balance and impedance

- Transformerless 2-4 wire conversion

- Constant current with constant voltage fallback for long loop capability

- Pin compatible with MH88632, MH88620 and MH88628

- Unbalanced detection (Tip, Ring ground sensing)

- · Auto ring trip with zero crossing

- On-Hook transmission (ANI) capability

- Compatible with requirements of CCITT, DOC/FCC and CSA/UL

- Excellent power dissipation (SIL vertical mounting)

- 12/16kHz meter pulse injection control

- Solid State TIP/RING reversals

- · Ringing amplifier

Ordering Information

MH88628 40 Pin SIL Package

0°C to 70°C

# **Applications**

- On/Off Premise PBX Line Cards

- DID (Direct Inward Dial) Line Cards

- Central Office Line Cards

# Description

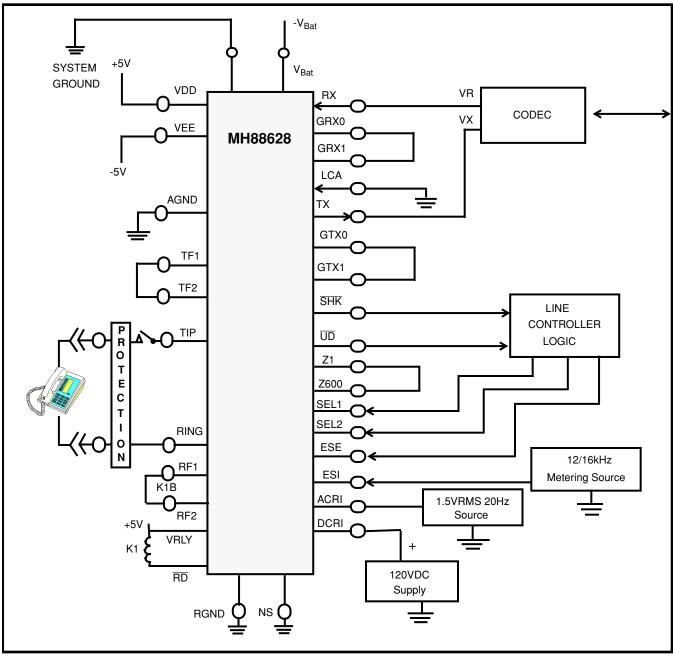

The Zarlink MH88628 SLIC provides all of the functions required to interface 2-wire off premise subscriber loops to a serial TDM, PCM, switching network of a modern PBX. The MH88628 is manufactured using thick-film hybrid technology which offers high voltage capability, reliability and high density resulting in significant printed circuit board area savings. A complete C.O. line card can be implemented with very few external components.

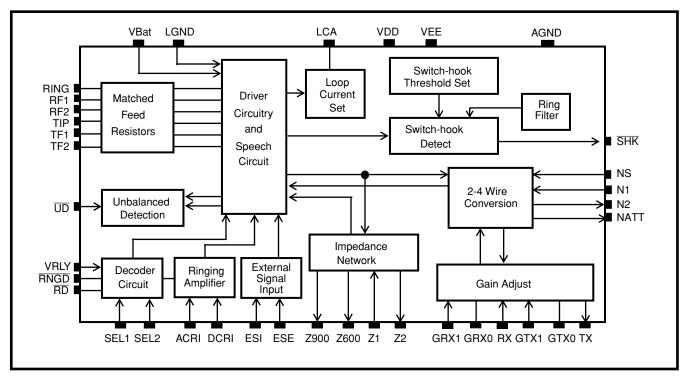

Figure 1 - Functional Block Diagram

1

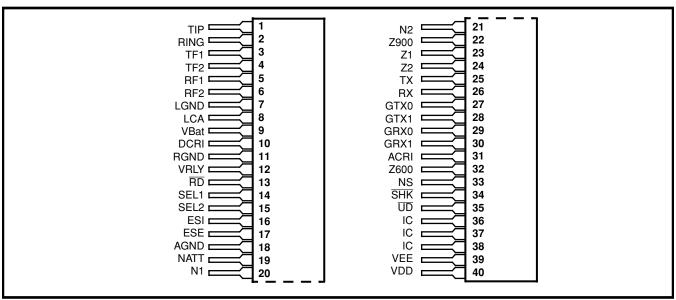

Figure 2 - Pin Connections

# **Pin Description**

| Pin # | Name | Description                                                                                                                                                                                                                                                                                                  |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | TIP  | Tip Lead. Connects to the "Tip" lead of subscriber line.                                                                                                                                                                                                                                                     |

| 2     | RING | Ring Lead. Connects to the "Ring" lead of the subscriber line.                                                                                                                                                                                                                                               |

| 3     | TF1  | Tip Feed 1. Access point for balanced ringing. Normally connects to TF2.                                                                                                                                                                                                                                     |

| 4     | TF2  | Tip Feed 2. Access point for balanced ringing. Normally connects to TF1.                                                                                                                                                                                                                                     |

| 5     | RF1  | Ring Feed 1. Access point for balanced ringing. Normally connects to RF2.                                                                                                                                                                                                                                    |

| 6     | RF2  | Ring Feed 2. Access point for balanced ringing. Normally connects to RF1.                                                                                                                                                                                                                                    |

| 7     | LGND | Battery Ground. VBat return path. Connected to system's energy dumping ground.                                                                                                                                                                                                                               |

| 8     | LCA  | Current Limit Set (Input). The current limit is set by connecting an external resistor to ground. For 30mA default current, this pin is tied to GND.                                                                                                                                                         |

| 9     | VBat | Battery Voltage. Typically -48Vdc is applied to this pin.                                                                                                                                                                                                                                                    |

| 10    | DCRI | DC Ringing Voltage Input. A continuous 120Vdc is applied to this input.                                                                                                                                                                                                                                      |

| 11    | RGND | Relay Driver Ground Connection.                                                                                                                                                                                                                                                                              |

| 12    | VRLY | Relay Supply Voltage Connection.                                                                                                                                                                                                                                                                             |

| 13    | RD   | Ring Drive (Output). Connects to ring relay coil.                                                                                                                                                                                                                                                            |

| 14    | SEL1 | Select 1 (Input). Refer to Table 5                                                                                                                                                                                                                                                                           |

| 15    | SEL2 | Select 2 (Input). Refer to Table 5.                                                                                                                                                                                                                                                                          |

| 16    | ESI  | External Signal Input. 12/16kHz meter pulse input.                                                                                                                                                                                                                                                           |

| 17    | ESE  | External Signal Enable. Applies the external signal to the line.                                                                                                                                                                                                                                             |

| 18    | AGND | Analog Ground. VDD and VEE return path.                                                                                                                                                                                                                                                                      |

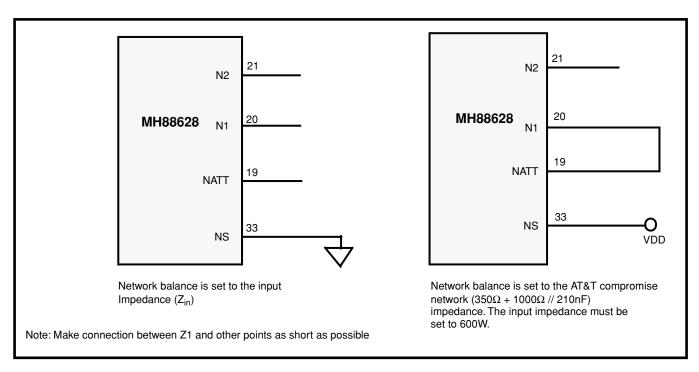

| 19    | NATT | <b>Network Balance AT+T Node.</b> Connects to N1 for a network balance impedance of AT&T compromise ( $350\Omega + 1k\Omega$ // $210nF$ ); the device's input impedance must be set to $600\Omega$ . This node is active only when NS is at logic high. This node should be left open circuit when not used. |

# Pin Description (continued)

| Pin #    | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

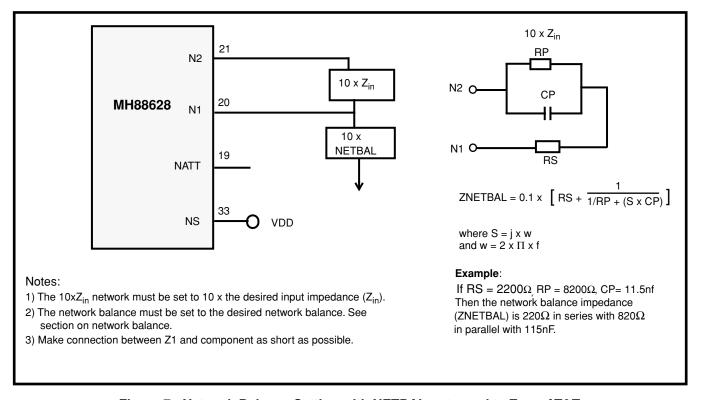

| 20       | N1   | <b>Network Balance Node 1(Input).</b> 0.1 times the impedance between pins N1 and N2 must match the device's input impedance, while 0.1 times the impedance between pins N1 and AGND is the device's network balance impedance. This node is active only when NS is at logic high. This node may be terminated when not used (i.e., NS at logic low).                                                                                                |  |  |  |

| 21       | N2   | Network Balance Node 2 (Output). See N1 for description.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

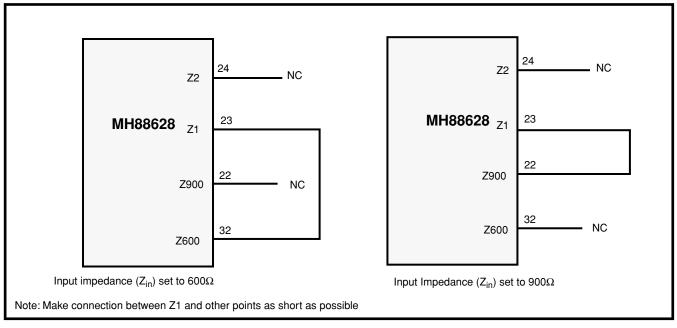

| 22       | Z900 | <b>Line Impedance 900</b> $\Omega$ <b>Node.</b> Connects to Z1 for a line impedance of 900 $\Omega$ . This node should be left open circuit when not used.                                                                                                                                                                                                                                                                                           |  |  |  |

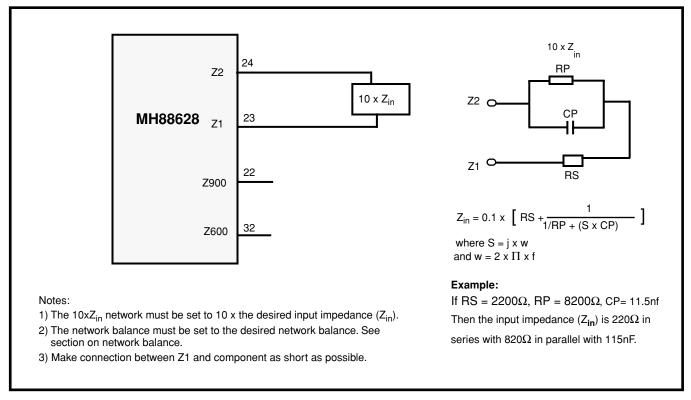

| 23       | Z1   | <b>Line Impedance Node 1 (Input)</b> . 0.1 times the times the impedance between pins Z1 and Z2 is the device's line impedance. This node must always be connected.                                                                                                                                                                                                                                                                                  |  |  |  |

| 24       | Z2   | <b>Line Impedance Node 2 (Output).</b> 0.1 times the times the impedance between pins Z1 and Z2 is the device's line impedance. This node should be left open circuit when not used.                                                                                                                                                                                                                                                                 |  |  |  |

| 25       | TX   | Transmit (Output). 4-Wire (AGND) referenced audio output.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 26       | RX   | Receive (Input). 4-Wire (AGND) referenced audio input.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 27       | GTX0 | Transmit Gain Node 0. Connects to GTX1 for 0dB transmit gain.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 28       | GTX1 | Transmit Gain Node 1. A resistor to AGND provides transmit gain adjustment.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 29       | GRX0 | Receive Gain Node 0. Connects to GRX1 for 0dB gain.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 30       | GRX1 | Receive Gain Node 1. A resistor to AGND provides receive gain adjustment.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 31       | ACRI | AC Ringing Voltage Input. A 1.5Vrms 20Hz signal is applied to this input.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 32       | Z600 | <b>Line Impedance 600</b> $\Omega$ <b>Node (Output).</b> Connects to Z1 for a line impedance of 600 $\Omega$ . This pin should be left open circuit when not used.                                                                                                                                                                                                                                                                                   |  |  |  |

| 33       | NS   | <b>Network Balance Setting (Input).</b> The logic level at NS selects the network balance impedance. A logic 0 enables an internal balance equivalent to the input impedance ( $Z_{in}$ ). While a logic 1 enables an external balance 0.1 times the impedance between pins N1 and AGND balanced to 0.1 times the impedance between pins N1 and N2. The impedance between N1 and N2 must be equivalent to 10 times the input impedance ( $Z_{in}$ ). |  |  |  |

| 34       | SHK  | Off-Hook Indication (Output). A logic low output indicates when the subscriber equipment has gone Off-Hook.                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 35       | ŪD   | <b>Unbalance Detect (Output).</b> A log IC low output indicates when the DC current flow in the Tip and Ring leads is unbalanced, indicating that the subscriber equipment has grounded the Ring lead.                                                                                                                                                                                                                                               |  |  |  |

| 36,37,38 | IC   | Internal Connection. These pins are internally connected and must be left open                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 39       | VEE  | Negative Supply Voltage5V dc.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 40       | VDD  | Positive Supply Voltage. +5V dc.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

# **Absolute Maximum Ratings\***

|   | Parameter           | Sym               | Min  | Max  | Units | Comments          |

|---|---------------------|-------------------|------|------|-------|-------------------|

| 1 | Supply Voltage      | $V_{Bat}$         | +0.3 | 65   | V     | With respect LGND |

|   |                     | $V_{DD}$          | -0.3 | 6    | V     |                   |

|   |                     | V <sub>EE</sub>   | +0.3 | -6   | V     |                   |

|   |                     | V <sub>DCRI</sub> | -0.3 | 140  | V     |                   |

| 2 | Storage Temperature | T <sub>S</sub>    | -40  | +125 | °C    |                   |

<sup>\*</sup> Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

# **Recommended Operating Conditions**

|   | Parameter             | Sym        | Min   | Тур* | Max   | Units | Comments |

|---|-----------------------|------------|-------|------|-------|-------|----------|

| 1 | Supply Voltage        | $V_{Bat}$  | -44   | -48  | -60   | V     |          |

|   |                       | $V_{DD}$   | 4.75  | +5.0 | 5.25  | V     |          |

|   |                       | $V_{EE}$   | -4.75 | -5.0 | -5.25 | V     |          |

| 2 | Operating Temperature | $T_{OP}$   | 0     | 20   | 70    | °C    |          |

| 3 | AC Ring Generator     |            |       |      |       |       |          |

|   | Voltage               |            |       | 90   |       | Vrms  |          |

|   | Frequency             |            | 17    |      | 33    | Hz    |          |

| 4 | DCRI                  |            |       |      |       |       |          |

|   | Input DC Voltage      | $V_{DCRI}$ | 110   | 120  | 130   | Vdc   |          |

<sup>\*</sup> Typical figures are at  $25^{\circ}$  C with nominal  $\pm$  5V supplies for design aid only.

# DC Electrical Characteristics<sup>‡</sup>

|   |              | Characteristics                                          | Sym                                                         | Min | Typ*            | Max      | Units                    | Test Conditions                                                                         |

|---|--------------|----------------------------------------------------------|-------------------------------------------------------------|-----|-----------------|----------|--------------------------|-----------------------------------------------------------------------------------------|

| 1 |              | Operating Loop Current  Var in loop current from nominal | I <sub>Loop</sub><br>I <sub>Loop</sub><br>I <sub>Loop</sub> | 16  | 45<br>30<br>± 2 |          | mA<br>mA<br>mA<br>mA     | $R_{Loop}$ =0 $\Omega$<br>2300 $\Omega$ VBat =-48V<br>$R_{Loop}$ =0 $\Omega$ , LCA -GND |

| 2 |              | Operating Currents                                       | I <sub>Bat</sub>                                            |     | 32<br>2         |          | mA<br>mA                 | R <sub>Loop</sub> =0 (off Hook),<br>LCA=GND<br>R <sub>Loop</sub> = open (On-            |

|   |              |                                                          | I <sub>DD</sub><br>I <sub>EE</sub>                          |     | 25<br>25        |          | mA<br>mA                 | Hook) On-hook or Off-Hook On-Hook or Off- Hook                                          |

| 3 |              | Power Dissipation                                        | PD <sub>O</sub><br>PD₁                                      |     | 2<br>300        |          | W<br>mW                  | Active<br>Standby/Idle                                                                  |

| 4 | SHK<br>UD    | Low level Output Voltage<br>High Level Output Voltage    | V <sub>OL</sub><br>V <sub>OH</sub>                          | 3.7 |                 | 0.5      | V<br>V                   | $I_{OL} = 400 \mu A$ $I_{OH} = 40 \mu A$                                                |

| 5 | SEL1<br>SEL2 | Low Level Input Voltage<br>High Level Input Voltage      | V <sub>IL</sub><br>V <sub>IH</sub>                          | 2.4 |                 | 0.8      | V<br>V                   |                                                                                         |

| 6 | ESE<br>NS    | High Level Input Current<br>Low Level Input Current      | I <sub>IH</sub><br>I <sub>IL</sub>                          |     |                 | 20<br>20 | μ <b>Α</b><br>μ <b>Α</b> | V <sub>IH</sub> =5.0V<br>V <sub>IL</sub> =0.0V                                          |

DC Electrical Characteristics are over recommended operating conditions unless otherwise stated.

Typical figures are at 25° C with nominal ±5V supplies and are for design aid only.

#### AC Electrical Characteristics<sup>‡</sup>

|    | Characteristics                                          | Sym                                | Min            | Тур*           | Max  | Units                  | Test Conditions                                                                    |

|----|----------------------------------------------------------|------------------------------------|----------------|----------------|------|------------------------|------------------------------------------------------------------------------------|

| 1  | TX Gain                                                  |                                    |                | 0              |      | dB                     | externally adjustable                                                              |

| 2  | RX Gain                                                  |                                    |                | 0              |      | dB                     | externally adjustable                                                              |

| 3  | Ringing Capability                                       |                                    |                | 5              |      | REN                    |                                                                                    |

| 4  | On-Hook Transmission<br>Signal Input Level<br>Gain       |                                    |                | 6              | 2.0  | V <sub>rms</sub><br>dB | $V_{Bat}$ =-48V<br>T-R load = 10k $\Omega$ min.                                    |

| 5  | External Signal Output Level                             |                                    | 1.75           |                | 2.25 | V <sub>rms</sub>       | $V_{\text{Bat}}$ = -48V, T-R load= 200 $\Omega$ LCA=0V, Zo-600 $\Omega$ , Gain=0dB |

| 6  | SHK Rise Time<br>Fall time                               | t <sub>R</sub><br>t <sub>F</sub>   |                | 1<br>1         |      | ms<br>ms               | Dial Pulse Detection                                                               |

| 7  | 2-Wire Termination<br>Impedance                          |                                    |                | 600/<br>900    |      | Ω                      | Selectable                                                                         |

| 8  | Off-Hook Detect Threshold                                |                                    |                | 10             |      | mA                     |                                                                                    |

| 9  | 2-Wire Return Loss                                       |                                    | 20<br>20<br>20 |                |      | dB<br>dB<br>dB         | 300 to 500Hz<br>500 to 2500Hz<br>2500 to 3400Hz                                    |

| 10 | Longitudinal Balance<br>Longitundinal to Metallic        |                                    | 58<br>53       |                |      | dB<br>dB               | 200-1000Hz<br>1kHz - 3k4Hz                                                         |

| 11 | Longitudinal Current<br>Capability                       |                                    |                |                | 40   | mA                     | 20mA per lead                                                                      |

| 12 | Idle channel Noise<br>Rx to T-R<br>T-R to Tx             | N <sub>CR</sub><br>N <sub>CX</sub> |                | 8<br>12        |      | dBrnC<br>dBrnC         |                                                                                    |

| 13 | Transhybrid Loss                                         | THL                                | 22             | 40             |      | dB                     | 200-3400Hz                                                                         |

| 14 | Unbalanced Detect Threshold                              | I <sub>UB</sub>                    |                | 10             |      | mA                     |                                                                                    |

| 15 | Analog Signal Overload Level<br>At Tip and Ring          |                                    |                |                | 4    | dBm                    | T-R=600Ω, V <sub>Bat</sub> =-48V                                                   |

| 16 | Ringing Signal Voltage                                   |                                    |                | 90             |      | Vrms                   |                                                                                    |

| 17 | Ringing Frequency                                        |                                    | 17             |                | 33   | Hz                     |                                                                                    |

| 18 | Ring Trip Delay                                          |                                    |                | 100            |      | ms                     |                                                                                    |

| 19 | Absolute Gain, Variation                                 |                                    |                | <u>+</u> 0.1   |      | dB                     | 0dB at T-R, 1kHz                                                                   |

| 20 | Relative Gain, reference to 1kHz                         |                                    |                | <u>+</u> 0.05  |      | dB                     | 300-3400Hz                                                                         |

| 21 | Power Supply Rejection Ratio $V_{Bat}$ $V_{DD}$ $V_{EE}$ | PSRR                               |                | 24<br>24<br>24 |      | dB                     | 1kHz, 100mVpp                                                                      |

<sup>\*</sup> Typical figure are at 25°C with nominal ±5V supplies and are for design aid only.

#### Notes:

Notes: Impedance set by external network of  $600\Omega$  or  $900\Omega$  default. External network for test purposes consists of  $2200\Omega + 8200\Omega$  // 11.5nF between pins Z1 and Z2, the equivalent Zin has  $1/10^{th}$  the impedance and is equivalent o  $220\Omega + 820\Omega$  // 11.5nF. Test condition uses a Zin value of  $600\Omega$ ,  $900\Omega$  and the above external network. Test conditions use a transmit and receive gain set to 0dB default and a Zin value of  $600\Omega$  unless otherwise stated. "Ref" indicates reference impedance which is equivalent to the termination impedance. "Net" indicates network balance impedance. Refer to Table 1, 2 for TX, RX gain adjustment.

<sup>‡</sup> AC Electrical Characteristics are over recommended operating conditions unless otherwise stated.

# **Functional Description**

The SLIC uses a transformerless electronic 2-wire to 4-wire conversion which can be connected to a Codec to interface the 2 wire subscriber loops to a time division multiplexed (TDM) pulse code modulated (PCM) digital switching network. For analog applications, the Tx and Rx of the 2-4 wire converter can be connected directly to an analog crosspoint switch such as the MT8816. Powering of the line is provided through precision battery feed resistors. The MH88628 also contains control, signalling and status circuitry which combines to provide a complete functional solution which simplifies the manufacture of line cards. This circuitry is illustrated in the functional block diagram in Fig. 1. The MH88628 is designed to be pin compatible with Zarlink's MH88632 and MH88625. This allows a common PCB design with common gain, input impedance and network balance.

# **Approvals**

FCC part 68, CCITT, DOC CS-03, UL 1459, CAN/CSA 22.2 No.225-M90 and ANSI/EIA/TIA-464-A are system level safety standards and performance requirements. As a component of a system, the MH88628 is designed to comply with the applicable requirements of these specifications.

### **Battery Feed**

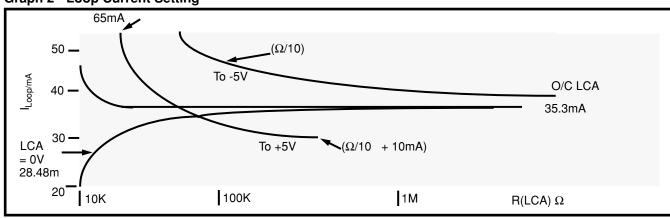

The loop current for the subscriber equipment is sourced through a pair of matched  $200\Omega$  resistors connected to the Tip and Ring. The two wire loop is biased such that the Ring lead is 2V above VBat (typically -46V) and the Tip lead is 2V below LPGD (typically -2V) during constant voltage, constant current mode.

The SLIC is designed for a nominal battery voltage of -48Vdc and can provide the maximum loop current of 45mA under the condition.

The MH88628 is designed to operate down to a minimum of 16mA dc, with a battery voltage of -44V. The Tip and Ring output drivers can operate within 2V of  $V_{Bat}$  and LGND rails. This permits a maximum loop range of  $2300\Omega$ .

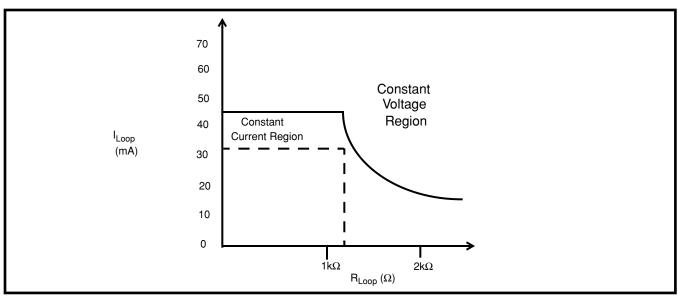

The MH88628 SLIC is a constant current with constant voltage fallback design. This design feature provides for long loop capability regardless of the constant current setting. Refer to Graph 1.

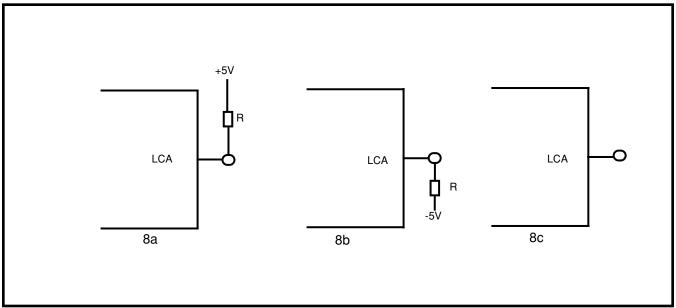

The LCA (Loop Current Adjust) pin is an input to an internal resistor divider network which generates a bias voltage. The loop current is proportional to this voltage. The loop current can be set between 20 and 45mA by various connections to the LCA pin as illustrated in Table 5 and Figure 8. The loop current during a fault condition will be limited to a safe level. Primary over-current protection is inherent in the current limiting feature of the  $200\Omega$  battery feed resistors. Refer to Graph 1.

#### **Receive and Transmit Audio Path**

The audio signal of the 2-wire side is sensed differentially across the external  $200\Omega$  feed resistors and is passed on to a second differential amplifier stage in the 2W/4W conversion block. This block sets the transmit gain on the 4-wire side and cancels signals originating from the receive input before outputting the signal.

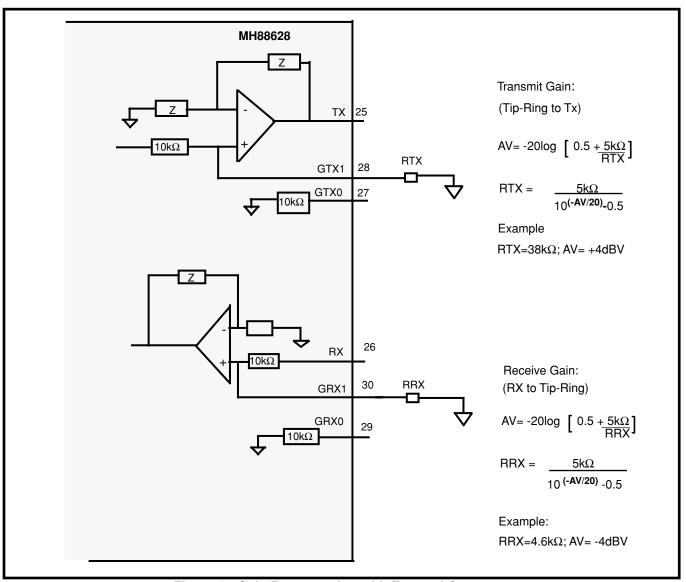

# **Programmable Transmit and Receive Gain**

Transmit Gain (Tip-Ring to Tx) and Receive Gain (Rx to Tip-Ring) are programmed by connecting external resistors (RRX and RRT) from GRXI to AGND and from GTX1 to AGND as indicated in Figure 3 and Tables 1 and 2. The programmable gain range is from -12dB to +6dB; this wide range will accommodate any loss plan. Alternatively, the default Receive Gain of 0dB and Transmit Gain of 0dB can be obtained by connecting GRX0 to GRX1 and GTX0 to GTX1. In addition, a Receive gain of +6dB and Transmit Gain of +6dB can be obtained by not connecting resistors RRX and RTX. For correct gain programming, the MH88628's Tip-Ring impedance (Z<sub>in</sub>) must match the line termination impedance.

For optimum performance, resistor RRX should be physically located as close as possible to the GRX1 input pin, and resistor RTX should be physically located as close as possible to the GTX1 input pin.

#### **Loop Current Setting**

**Graph 1 - ILoop/RLoop Characteristics**

# Two wire Port Termination Impedance

The AC termination impedance of 600 or  $900\Omega$ , of the 2W port, is set using active feedback paths to give the desired relationship between the line voltage and the line current. The loop current is sensed differentially across the two feed resistors and converted to a single ended signal. This signal is fed back to the Tip/Ring driver circuitry such that impedance in the feedback path gets reflected to the two wire port. The MH88628's Tip-Ring impedance  $(Z_{in})$  can be set to  $600\Omega$ ,  $900\Omega$  or to a user selectable value. Thus, Zin can be set to any international requirement. The connection to Z1 determines the input impedance. With Z1 connected to Z600, the line impedance is set to  $600\Omega$ . With Z1 connected to Z900, the line impedance is set to  $900\Omega$ . A user defined impedance can be selected which is 0.1 times the impedance between Z1 and Z2.

For example, with  $2200\Omega$  in series with 11.5nF in parallel with  $8200\Omega$ , all between Z1 and Z2, the devices line impedance will be  $220\Omega$  in series with 115nF in parallel with  $820\Omega$ . See Table 3 and Figures 4 & 5.

#### **Network Balance**

Transhybrid loss is maximized when the line termination impedance and SLIC network balance are matched. The MH88628's network balance impedance set can be set to Zin, AT&T ( $350\Omega + 1k\Omega$  //210nF) or to a user selectable value. Thus, the network balance impedance can be set to any international requirement, A logic level control input NS selects the balance mode. With NS at logic low, an internal network balance impedance is matched to the line impedance ( $Z_{in}$ ). With NS at logic high, a

user defined network balance impedance is selected which is 0.1 times the impedance between N1 and AGND. For example, with  $2200\Omega$  in series with 11.5nF in parallel with  $8200\Omega$ , all between N1 and AGND, and NS at logic high, the devices network balance impedance is  $220\Omega$  in series with 115nF in parallel with  $820\Omega$ ; the impedance between N1 and N2 must be equivalent to 10 times the input impedance ( $Z_{in}$ ). In addition, with NS at logic high, an AT&T network balance impedance can be selected by connecting NATT to N1; in this case, no additional network is required between N1 and N2. See Table 4 and Figure 6.

#### 12/16kHz Meter Pulse

The MH88628 provides control of an external signal path to the driver. A 12/16kHz continuous signal can be applied to the ESI pin. Control of the ESE input allows the metering signal to be transmitted to the line.

#### **Unbalanced Detection**

The Unbalanced Detect (\$\overline{UD}\$) pin goes low when the DC current through the two battery feed resistors is unbalanced i.e., when the average DC current into the Ring lead exceeds the current flow out of the Tip lead (indicating that the Ring lead has been grounded).

When the SLIC is interfaced to ground start subscriber equipment during the idle state, the  $\overline{\text{UD}}$  output is monitored for indication of the subscribers Ring Ground signal. The maximum loop current supplied by the feed circuitry under this condition is limited.

#### **Longitudinal Balance**

The longitudinal balance specifies the degree of common mode rejection in the 2 to 4 wire direction. Precision laser trimming of internal resistors in the hybrid ensures good overall longitudinal balance.

The interface circuitry can operate in the presence of induced longitudinal currents of up to 40mA at 60Hz.

#### Off-Hook and Dial Pulse Detection

The SHK pin goes low when the DC-loop current exceeds a specified level. The threshold level is internally set by the bias voltage of the switch-hook detect circuitry. Dial pulse can be detected by monitoring the interruption rate at the SHK pin. These dial pulses would be debounced by the

# **Ring Trip Detection**

The interface permits detection of an Off-Hook condition during the ringing. If the subscriber set goes Off-Hook when the ringing signal has been applied, the DC loop current flow will be detected within approx. 100msecs and the SHK output will go low. The ring relay is automatically disabled by the internal hardware.

#### **Control Decode**

The different modes of operation are selected by decoding the SEL1 and SEL2 inputs (see Table 5).

#### **DTMF**

The DTMF tones are transmitted and received at the

Figure 3 - Gain Programming with External Components

Figure 4 - Input Impedance (Z $_{\text{in}}$ ) Settings with Z $_{\text{in}}$  equal to 600 or 900  $\!\Omega$

Figure 5 - Input Impedance (Z $_{in}$ ) Settings with Z $_{in}$  not equal to 600 to 900 $\Omega$

Figure 6 - Network Balance Setting with NETBAL equal to Zin or AT&T

Figure 7 - Network Balance Setting with NETBAL not equal to  $\mathbf{Z}_{\text{in}}$  or AT&T

Tables 1 & 2: Transmit and Receive Gain Programming

| Transmit<br>Gain (dB)               | RTX Resistor Value (Ω)                             | Notes                                                                                                                                              |

|-------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| +6.0                                | No Resistor                                        |                                                                                                                                                    |

| +4.0                                | 38.3k                                              | Results in 0dB overall gain when used with Zarlink A-law codec (i.e. MT8965)                                                                       |

| +3.7                                | 32.4k                                              | Results in 0dB overall gain when used with Zarlink $\mu$ -law codec (i.e. MT8964)                                                                  |

| 0.0                                 | GTX0 to GTX1                                       |                                                                                                                                                    |

| -3.0                                | 5.49k                                              |                                                                                                                                                    |

| -6.0                                | 3.32k                                              |                                                                                                                                                    |

| -12.0                               | 1.43k                                              |                                                                                                                                                    |

|                                     |                                                    |                                                                                                                                                    |

| Receive Gain<br>(dB)                | RRX Resistor<br>Value (Ω)                          | Notes                                                                                                                                              |

|                                     |                                                    | Notes                                                                                                                                              |

| (dB)                                | Value (Ω)                                          | Notes                                                                                                                                              |

| (dB)<br>+6.0                        | Value (Ω)<br>No Resistor                           | Notes                                                                                                                                              |

| +6.0<br>0.0                         | Value (Ω)  No Resistor  GRX0 to GRX1               | Notes  Results in 0dB overall gain when used with Zarlink A-law codec (i.e. MT8965)                                                                |

| +6.0<br>0.0<br>-3.0                 | Value (Ω)  No Resistor  GRX0 to GRX1  5.49k        | Results in 0dB overall gain when used with Zarlink A-law codec (i.e.                                                                               |

| (dB)<br>+6.0<br>0.0<br>-3.0<br>-3.7 | Value (Ω)  No Resistor  GRX0 to GRX1  5.49k  4.87k | Results in 0dB overall gain when used with Zarlink A-law codec (i.e. MT8965)  Results in 0dB overall gain when used with Zarlink μ-law codec (i.e. |

Note 1: See Figures 3 and 4 for additional details.

Note 2: Overall gain refers to the receive path of PCM to 2-wire, and transmit path of 2-wire to PCM.

**Table 3: Input Impedance Settings**

| Z2            | <b>Z</b> 1             | Z600       | Z900                | Resulting input impedance (Z <sub>in</sub> ) |

|---------------|------------------------|------------|---------------------|----------------------------------------------|

| NA            | Connect 2              | 11 to Z600 | NA                  | $600\Omega$                                  |

| NA            | Connect Z1 to<br>Z9000 | NA         | Connect Z1 to Z900' | 900Ω                                         |

| Connect netwo | rk from Z1 to Z2       | NA         | NA                  | 0.1 x impedance between Z1 & Z2              |

Note 1: NA indicates high impedance ( $10k\Omega$ ) connection to this pin does not effect the resulting network balance. Note 2: See Figure 4 & 5 for Application Circuits.

**Table 4: Network Balance Settings**

| NS (Input) | N2                                                                             | N1                        | NATT           | Resulting input impedance (Z <sub>in</sub> )                                                  |

|------------|--------------------------------------------------------------------------------|---------------------------|----------------|-----------------------------------------------------------------------------------------------|

| Low        | NA                                                                             | NA                        | NA             | Equivalent to Z <sub>in</sub>                                                                 |

| High       | NA                                                                             |                           | ect N1<br>NATT | AT&T compromise (350 $\Omega$ + 1k $\Omega$ // 210nF)<br>$Z_{\text{in}}$ must be 600 $\Omega$ |

| High       | Connect networ<br>AGND equivaler<br>NETBAL. Conne<br>from N1 to N2 e<br>x Zin. | nt to 10 x<br>ect network | NA             | 0.1 x impedance between N1 & N2                                                               |

Note 1: NA indicates high impedance  $(10k\Omega)$  connection to this pin does not effect the resulting network balance.

Note 2: Low indicates Logic Low.

Note 3: See Figures 6 and 7 for Application Circuit.

Figure 8 - Loop Current Setting

# **High Voltage capability**

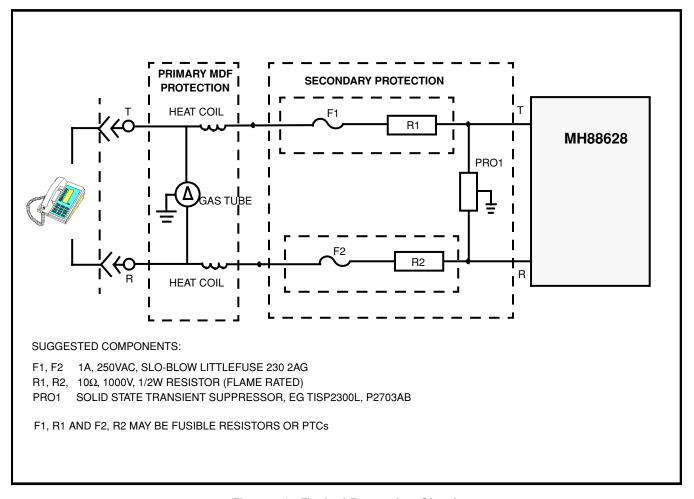

Inherent in the thick-film process is the ability of the substrate to handle high voltage. The standard Zarlink thick-film process provides dielectric strengths of greater than 1000VAC or 1500VDC. The thick-film process allows easy integration of surface mount components such as the high voltage bi-polar power transistor line drivers. This allows for simplier, less elaborate and less expensive protection circuitry required to handle high voltage transients and fault conditions caused by lightning, induced voltages and power line crossings.

#### **On-hook Transmission**

The MH88628 provides for on-hook transmission which supports features such as Automatic Numbers Identification (ANI). The (ANI) information is a FSK signal originating from and sent by the C.O. during the off period of the ringing voltage being sent to the subscribers set. The signal is present during the off period between the first and second ring. The subscribers set decodes the FSK signal and displays the calling party's number.

#### **TIP Disable**

A relay driver, controlled by SEL1 and SEL2, is provided to drive a relay which can be used to disable the TIP line when the MH88628 is used for a ground start central office interface.

#### Loop Length

The MH88628 can accommodate loop length of up to  $2300\Omega$  minimum (including the subscriber equipment). This corresponds to approximately 8km using 26AWG twisted pair or 15km using 24AWG twisted pair.

#### **Central Office Operation**

The MH88628 can be configured for ground start C.O. applications with the addition of Q1, D1 and K2, as shown in Figure 9. Ground start requires control of the Tip lead to remove battery ground from subscriber loop. For loop start applications, control of the Tip lead is not required.

C.O's perform Tip/Ring reversals to indicate that a tool call has been dialled. The Tip/ring reversal can indicate a toll diversion signal.

#### **Internal Ringing Amplifier Operation**

The MH88628 offers an on-board ringing amplifier. A 1.5 VRMS, 20Hz signal is amplified internally and applied to TIP and RING leads in a balanced configuration. A +120Vdc supply are applied continuously to the MH88628. The decode signals on SEL1 and SEL2 enable the ringing signal to the TIP and RING when required.

Figure 9 - OPS SLIC Configuration Applications Circuit - Normal Ringing

#### **Graph 2 - Loop Current Setting**

**Table 5: Control Decode Table**

| Mode | Condition                       | SEL1 | SEL:2 |

|------|---------------------------------|------|-------|

| 1    | Normal Operation                | 0    | 0     |

| 2    | Apply internal balanced ringing | 1    | 0     |

| 3    | Reverse TIP and RING            | 0    | 1     |

| 4    | Enable Relay Driver             | 1    | 1     |

**Table 6: Loop Current Setting**

| Loop<br>Current | Ref. Fig # | LCA Pin Connection           |

|-----------------|------------|------------------------------|

| 20              | 8a         | Connect 10kΩ from LCA to +5V |

| 25              | 8a         | Connect 22kΩ from LCA to +5V |

| 30              | 8a         | Connect 36kΩ from LCA to +5V |

| 35              | 8c         | LCA open circuit             |

| 40              | 8b         | Connect 24kΩ to -5V          |

| 45              | 8b         | Connect 10kΩ from LCA to -5V |

Figure 10 - Typical Protection Circuit

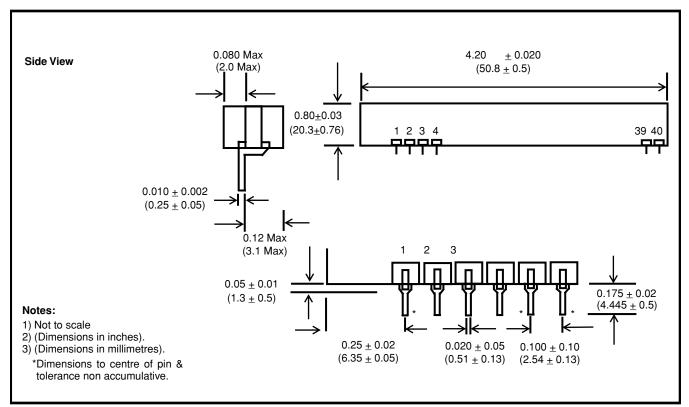

Figure 11 - Mechanical Data

# MH88628 Preliminary Information

Notes:

# For more information about all Zarlink products visit our Web Site at www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE